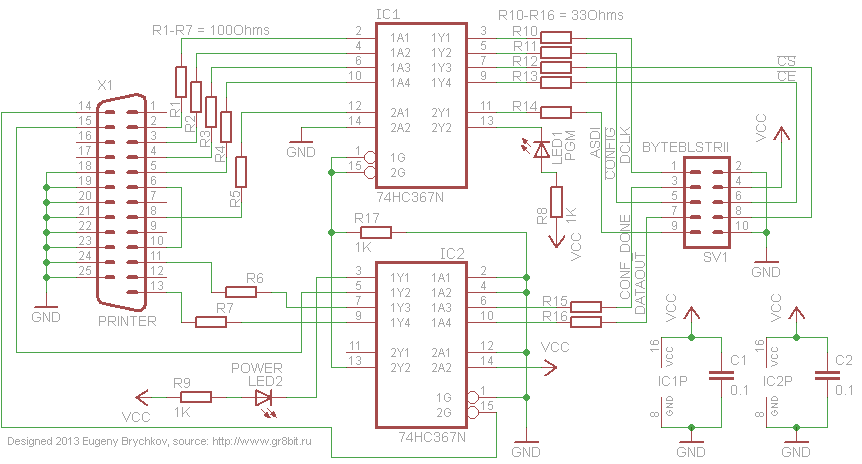

Of course this board provides JTAG interface. Meanwhile, JTAG has more priority than other configuration method. Usually All Altera FPGA can be configured via JTAG commands. The configured data of FPGA can be downloaded to target device with 3 methods, FPGA Active, FPGA Passive and JTAG, according to the role played in Configure Circuit. are controlled by configuration data, which is stored in FPGA RAM. Within the FPGA, many programmable multiplexers, logic, interconnect nodes and RAM initialization, etc. FPGA reconfigured at each reboot is a feature of SRAM-based FPGA. The schematic of the circuit:Īctive-low Reset, FPGA will be reconfigured, as soon as PROG_B pin restores to high levelĬonfiguration/Programming Interface Configuration is also known as loading and download. FPGA will be reconfigured without reboot when the nCONFIG key is pressed. While nCONFIG Reset Circuit is triggered by nCONFIG key.

RST reset Circuit is a RC reset Circuit with RESET button switch, which is pressed to generate a Reset-signal, active-low. Reset Circuit The Reset Circuit contains RST Reset Circuit and nCONFIG Reconfigure Circuit. A 50MHz crystal oscillator on board is used for supply accurate clock. We use a global clock interface CLK in our design, because it is single clock interface, we consider the use of active crystal clock as an external clock source. The shortest time span of GCLK can supply is used for delay. The FPGA has dedicated global clock pin, which is connected to each register of the device.

The schematic of the circuit:ģ.3V voltage, converted from AMS1117-3.3, is generally used to supply the voltage of clock, configure circuit, special features pin high, etc.Ģ.5V voltage, converted from AMS1117-2.5, is generally used to supply the voltage of VCCA.ġ.2V voltage, converted from AMS1117-1.2, is generally used to supply the voltage of VCCINT, VCC_PLL, etc.Ĭlock Circuit The best solution of FPGA clock circuit is: A main clock, which is driven by dedicated global clock input(GCLK), controls each timing device of the design. Meanwhile, a PWR LED is connected to 3.3V output, to meet the needs of checking power operation status. So for normal operation, the power supply of the board is designed for converting input voltage 5V to multiple voltages 3.3V, 2.5V, 1.2V. Then I/O banks power supply VCCO can be connected to 1.2V, 1.5V, 1.8V, 2.5V, 3.0V, 3.3V to supply each area with different voltage standards. Noting that EP4CE6 requires 1.0V/1.2V for Internal core supply voltage (VCCINT) and PLL digital power supply (VCCD_PLL), requires 2.5V for PLL analog power supply (VCCA). You can find voltage supplies details from the File:Cyclone-IV-Device-Handbook.pdf. Power Supply Circuit Power Supply Circuit is the basic circuit for normal operation. Then, how and why do the devices connect together? What are their functions?įramework of the Circuit Core-board-circuit framework is shown in the following figure:

#Altera usb blaster schematic pdf serial

There are voltage regulator AMS1117, serial FLASH memory EPCS16, crystal oscillator, JTAG interface, LEDs, buttons, etc., beside main FPGA. Go with you to witness how a chip evolves to a board. Hardware Design This chapter mainly about the basic idea of core-board hardware design. Overview Basic operation and demo user guide of Waveshare FPGA Altera serial board are in the present document for helping you quick start your FPGA development.

#Altera usb blaster schematic pdf windows

Link for schematic (page 19 shows the On-Board USB Blaster II) So I have got a new MAX II chip which I have soldered to the dev board and when using the USB cable to the board windows does recognize the uP which are on the dev board as USB interface the MAX II. BUT it's very slow (JTAG) compared to the on-board Blaster (which does load in parallel). The 2 chips was removed and all voltage went back to normal and the Cyclone V does work fine but need to be programmed with a external USB blaster, again that works fine. I have a Cyclone V GT FPGA Development Board The board had a broken MAX II and MAX V due to some short circuit some years ago and the MAX II and MAX V did short the voltage reg.